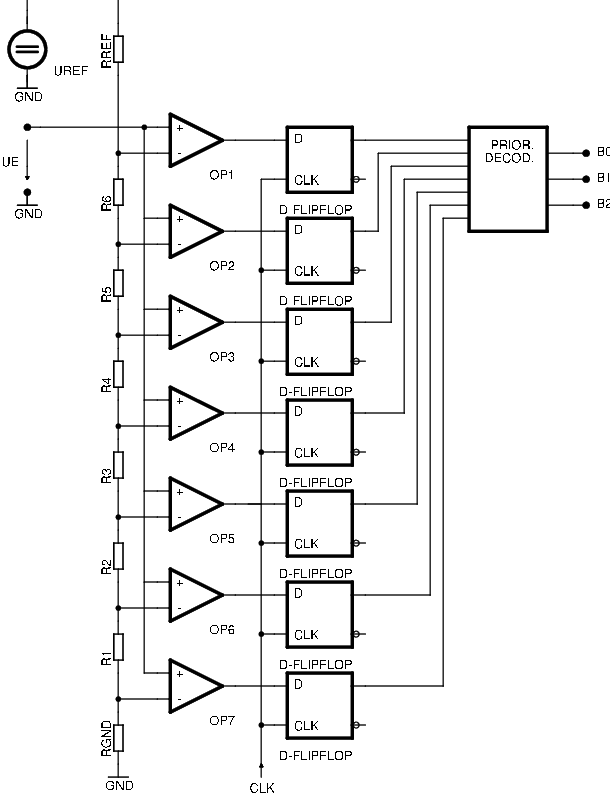

| Bild 5.5.: | Prinzip eines 3-Bit-Parallelumsetzers |

Im Folgenden sollen kurz die gängigsten Prinzipien der A/D-Wandlung vorgestellt werden. Viele dieser Prinzipien können (entweder direkt oder indirekt) auch mit dem MSP430 umgesetzt werden.

Die einfachste Realisierung eines A/D-Wandlers ist ein Parallelumsetzer. Das Prinzip dieser A/D-Wandlung basiert darauf, dass man für jede Quantisierungsstufe eine Referenzspannung generiert. Diese Referenzspannungen werden mit der zu erfassenden Spannung UE mit Hilfe von Komparatoren parallel verglichen. Wenn UE größer als die entsprechende Referenzspannung der Quantisierungsstufe ist, liefert der Komparator den Zustand 1. Ist die Spannung UE dagegen kleiner, liefert der Komparator den Zustand 0. Die Komparatorzustände müssen mit einer entsprechend ausgelegten Logik, einem so genannten Prioritätsdecoder ([TSG02] und [Feh07]), in eine binäre Zahl umgewandelt werden.

Schaltet man den Prioritätsdecoder direkt nach den Komparatoren, stellt man insbesondere bei zeitlich veränderlichen Messspannungen eine Vielzahl von fehlerhaften A/D-Werten fest, die weit über der akzeptablen Messungenauigkeit liegen können. Dieser Fehler basiert unter anderem darauf, dass die Signallaufzeiten der Komparatoren und des Prioritätsdekoders nicht gleich sind. Zumindest den Ungenauigkeiten des Prioritätsdekoders kann man vorbeugen, indem man diesem flankengetriggerte D-Flipflops vorschaltet und so die Komparatorzustände synchron verarbeiten kann (digitale Sample-and-Hold-Stufe). Das schaltungstechnische Prinzip eines 3-Bit-Parallelumsetzers ist in Bild 5.5 dargestellt. Das Ergebnis der A/D-Wandlung liegt dabei in Form der Bits B0, B1 und B2 nach dem Prioritätsdecoder vor. Die Widerstände wählt man mit Rx = R (mit x = 1...6) und RGND = RREF = R∕2.

Das Verfahren der Parallelumsetzung zeichnet sich dadurch aus, dass es für hohe Abtastfrequenzen eingesetzt werden kann. Damit erhält man eine hohe Bandbreite des A/D-Wandlers. Ein Nachteil ist der hohe schaltungstechnische Aufwand, insbesondere dann, wenn man die Auflösung des A/D-Wandlers erhöhen will. So steigt die Anzahl der benötigten Komparatoren exponentiell mit der Anzahl der Bits zur Darstellung des Signals [TSG02]. A/D-Wandler, die auf dem Prinzip der Parallelumsetzung basieren, werden daher in der Regel für Anwendungen mit hohen Abtastfrequenzen bei einer niedrigeren Auflösung eingesetzt.

Beim Wägeverfahren bzw. Zählverfahren werden, anders als beim Verfahren der Parallelumsetzung, die Referenzspannungen der Quantisierungsstufen sukzessive und damit nicht gleichzeitig für den Vergleich mit der zu erfassenden Spannung USIG erzeugt.

Eine schaltungstechnische Realisierung des Wägeverfahrens ist in Bild 5.6 dargestellt. Ein Abtast-Halte-Glied (Sample-and-Hold, „SAH“) hält die zu erfassende Spannung während der A/D-Wandlung zunächst konstant. Dies ist notwendig, da die Quantisierung wie gesagt ja nicht sofort und gleichzeitig erfolgt, sondern sequentiell.

Die Referenzspannung wird mit Hilfe eines Digital-Analog-Wandlers („D/A-Wandler“) erzeugt und dann mit der nach dem Abtaste-Halte-Glied anliegenden Spannung durch einen Komparator verglichen. Den Zustand des Komparators wertet das so genannte Successive-Approximation-Register, kurz SAR-Register aus.

Begonnen wird mit dem höchstwertigen Bit. Dies wird testweise im SAR-Register und damit auch

im D/A-Wandler gesetzt und der enstehende analoge Referenzwert mit der Eingangsspannung

verglichen. Ist der Vergleichswert höher, wird das Bit im SAR-Register gelöscht, wenn nicht,

bleibt es gesetzt. Nun erfolgt der Test mit dem nächsten Bit, so lange, bis jedes Bit

einmal geprüft wurde. Das Ergebnis der Wandlung steht demnach nach n Schritten

im SAR-Register zur Verfügung und kann dort ausgelesen werden. Zur Steuerung der

Taktfolge wird ein Taktsignal benötigt, das die zeitliche Abfolge der Vergleichsoperationen

auslöst.

Bild 5.7 skizziert diesen Vorgang nochmals grafisch. Zunächst wird das zu erfassende Signal USIG(t) zum Zeitpunkt T0 durch das Abtast-Halte-Glied konstant gehalten: USAH(t ≥ T0) = USIG(T0) = const. Das Signal wird dann sukzessive durch die D/A-Wandler- Spannung UDA(t) approximiert.

Das Wägeverfahren benötigt nur relativ wenige und einfache Komponenten und damit im Vergleich weniger schaltungstechnischen Aufwand als die Parallelumsetzung. Daher wird es vielfach für Low-Cost-A/D-Wandler eingesetzt. Ein Nachteil ist, dass die erreichbaren Abtastfrequenzen durch den iterativen Prozess und die erforderlichen Einschwingzeiten von Komparator und D/A-Wandler limitiert sind.

Anders als beim Wägeverfahren wird das zu erfassende Signal beim Rampenverfahren nicht direkt ausgewertet, sondern indirekt durch eine dazu äquivalente Größe: der Zeit. Das Rampenverfahren ist damit im Gegensatz zur Parallelumsetzung und zum Wägeverfahren eine indirekte Methode zur A/D-Wandlung. Ein Problem des im vorigen Abschnitt beschriebenen Wägeverfahrens ist der hohe Anspruch an die Genauigkeit des D/A-Wandlers zur Erzeugung der Referenzspannungen der Quantisierungsstufen. Die im Folgendem beschriebenen Rampenverfahren umgehen dieses Problem, indem der D/A-Wandler durch eine Integration einer konstanten Referenzspannung ersetzt wird und stattdessen Integrationszeiten tm ausgewertet werden.

Wie wir im Folgenden noch sehen werden, werden Single- und Dual-Slope-A/D-Wandler auf Grund der limitierten Abtastfrequenz bei gleichzeitig sehr einfachem Aufbau bevorzugt im untersten Low-Cost-Segment bei einfachsten Anforderungen an die A/D-Wandlung verwendet.

Beim Single-Slope- oder auch Ein-Rampen-Verfahren wird die Zeit gemessen, die benötigt wird, bis die vom Integrator gelieferte Spannung größer oder gleich der zu erfassenden Signalspannung ist. Unter der Voraussetzung, dass der Spannungsanstieg durch Integration linear erfolgt, sind Zeit und Spannung zueinander proportional. Das schaltungstechnische Prinzip des Single-Slope-Verfahrens ist in Bild 5.8 dargestellt.

Die Messzeit tm wird mit Hilfe eines Zählerregisters CNT bestimmt, indem die Impulse eines Rechteck- oder Impulsgenerators seit Start der Integration gezählt werden. Wenn die Signalspannung der Spannung des Integrators entspricht, leitet der Komparator den Zustand 1 an das Zählerregister CNT weiter. Daraufhin wird der Zählvorgang abgebrochen und das zur Eingangsspannung äquivalente digitale Wort Z kann an die nachfolgende Peripherie oder einen Mikroprozessor weitergegeben werden. Außerdem sendet das Zählerregister einen Impuls an die Steuereinheit STR, die dafür sorgt, dass der Kondensator C entladen und der Integrator wieder in den Grundzustand zurückgeführt wird, um eine erneute A/D-Wandlung vornehmen zu können.

UInt = ∫

0t URefdt URefdt | =  ⋅ URef ⋅ URef U

SIG U

SIG | (5.6) |

t1 = RC ⋅ | (5.7) |

Sind R und C sowie die Referenzspannung bekannt, kann über eine Messung der Zeit die Signalspannung quantifiziert werden. Die theoretisch erreichbare Auflösung bei gegebener Abtastfrequenz hängt dabei von der Dimensionierung des Widerstands R und des Kondensators C, aber insbesondere auch von der Breite des Zählerregisters CNT sowie dessen Taktfrequenz ab.

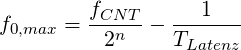

| (5.8) |

Die zusätzliche Latenzzeit TLatenz resultiert daraus, dass am Ende der Wandlung der Kondensator entladen werden muss, bevor eine neue Messung beginnen kann. Bei einer Taktfrequenz von 100MHz und einer Auflösung von 12 Bit wäre immerhin eine Abtastfrequenz von fast 25kHz möglich. In der Regel können hochfrequente Impulse sehr gut gezählt werden. Mit dem Ein-Rampen-Verfahren ist es daher möglich, sehr einfache und kostengünstige A/D-Wandler zu bauen. Ein Nachteil ist, dass sowohl die Referenzspannung als auch die Komponenten R und C das Wandlungsergebnis beeinflussen. Speziell letztere sind z.B. bei Temperaturveränderungen alles andere als konstant.

Das Dual-Slope-Verfahren oder auch Zwei-Rampen-Verfahren ist eine sehr häufig verwendete Methode zur A/D-Wandlung. Der Vorteil dieses Verfahrens ist der schaltungstechnisch geringe Aufwand und die Möglichkeit, hohe Auflösung im Vergleich zum Wägeverfahren zu erreichen. Anders als beim Single-Slope-Verfahren wird beim Dual-Slope-Verfahren sowohl eine Referenz- als auch die Eingangsspannung integriert. Dadurch kann man den Einfluss des Widerstands R und des Kondensators C auf die A/D-Wandlung elimieren. Dies ist speziell zur Kompensation temperaturbedingter Änderungen dieser Komponenten sehr gut geeignet.

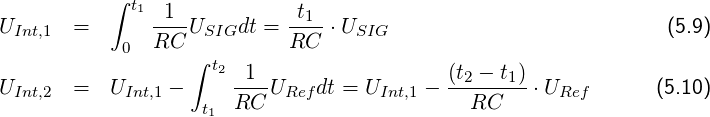

Beim Zwei-Rampen-Verfahren wird zunächst die Signalspannung USIG für eine bestimmte Zeit t1 integriert.

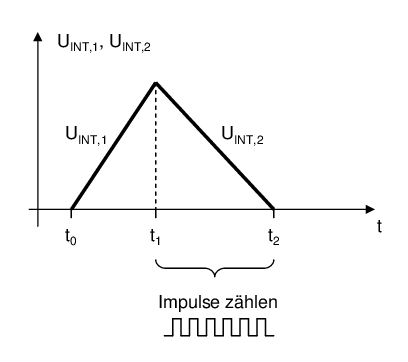

| Bild 5.9.: | Integration der Signalspannung und der gegenphasigen Referenzsspannung beim Dual-Slope-Verfahren. |

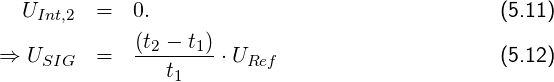

In Bild 5.9 wird die Integration durch die steigende Spannung UInt,1 dargestellt. Nach der Zeit t1 schaltet das Steuerwerk („STR“) auf die gegenphasig zur Signalspannung gepolte Referenzspannung -URef, welche nun ebenfalls integriert wird. Die dem Integral entsprechende Spannung ist UInt,2. Ab dem Zeitpunkt t1 wird so lange die Zeit gemessen, bis die Spannung UInt,2 durch den Nulldurchgang geht. Damit gilt:

Die Zeit t1 ist fest eingestellt und immer konstant. So lange USIG kleiner als URef bleibt, ist t2 - t1 < t1. Damit kann man das Zählerregister („CNT“) bis zu einem vorher festgelegten Zählwert hochzählen lassen, am besten genau bis zur Zweierpotenz, die der gewünschten Bit-Auflösung entspricht. Die Zeitdifferenz t2 - t1 wird dann einfach durch Herunterzählen von diesem Zahlenwert und anschließender Zweierkomplement-Umrechnung gemessen. Die daran anschließende Division durch t1 muss nicht einmal durchgeführt werden, da das Wandlungsergebnis ja nicht auf 1 normiert werden muss. Nach einem Zählzyklus wird das Ergebnis an die nachgeschaltete Peripherie oder den Mikroprozessor weitergeleitet. Das schaltungstechnische Prinzip des Dual-Slope-Verfahrens ist in Bild 5.10 dargestellt.

Das Steuerwerk STR schließt am Ende der Wandlung den Kondensator C kurz, um den Wandler so in den Anfangszustand für eine erneute Messung zurückzuversetzen.

Da Frequenzen mit digitalen Schaltungen recht einfach gemessen werden können, kann man eine A/D-Wandlung auch über eine Hilfsgröße wie die Frequenz eines Hilfssignals realisieren. In einem Spannungs/Frequenz-Umsetzer (U/F-Wandler) wird die Spannung durch eine Kombination aus einem Integrator und einem Schmitt-Trigger in eine Frequenz umgewandelt, Bild 5.11.

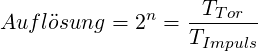

Die Frequenzmessung selbst ist recht einfach durch einen Zähler und einen Zeitgeber zu realisieren. Dabei hat man zwei Möglichkeiten: Entweder gibt der Zeitgeber die Torzeit vor, in der die eingehenden Impulse des U/F-Wandlers gezählt werden (Signale hoher Frequenz) oder der U/F-Wandler bestimmt die Torzeit und die Impulse des Zeitgebers werden gemessen (Signale niedriger Frequenz). Wichtig ist dabei, dass die Torzeit deutlich größer als die Periodendauer des Zählsignals ist, damit so auch eine entsprechende Auflösung der A/D-Umsetzung erreicht werden kann. Auf der anderen Seite entspricht die Torzeit der Abtastfrequenz der gesamten Wandleranordnung. Auflösung und Torzeit sind zueinander proportional, Gl. 5.13.

| (5.13) |

Für die Frequenzmessung kann natürlich auch ein MSP verwendet werden, wie wir es in Kapitel 4 als Beispiel ja schon gesehen haben.

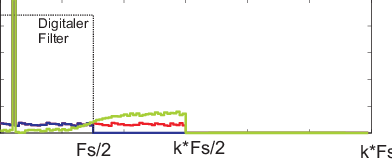

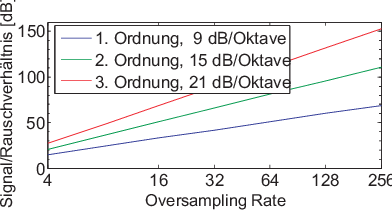

Wie wir in der theoretischen Einleitung (Kapitel 5.1) ja schon erörtert haben, kann man bei einem A/D-Wandler durch Oversampling die Auflösung erhöhen. Das Quantisierungsrauschen ist gleichverteilt im Bereich 0...FS/2. Durch Oversampling verteilt sich dieses auf einen größeren Frequenzbereich (die Signalenergie des Quantisierungsrauschens bleibt gleich), so dass man durch nachfolgende digitale Filterung des oberen Frequenzbereiches nur das Quantisierungsrauschen wegfiltern und so das Signal-zu-Rausch-Verhältnis SNR entsprechend verbessern kann. Bei Verdoppelung der Abtastfrequenz FS erreicht man ideal eine Verbesserung des SNR um 3dB (= 3dB/Oktave). Prinzipiell kann man dieses auch auf die Spitze treiben und nur einen 1-Bit-Wandler (Komparator) verwenden und die Auflösung alleine durch Oversampling erzeugen. Dieses Prinzip wird in einem Sigma-Delta-Wandler umgesetzt. Die direkte Umsetzung einfach mit einem Komparator scheitert jedoch daran, dass eine wesentliche Voraussetzung nicht erfüllt ist: Es liegt meist keine stochastische Gleichverteilung der Spannungswerte des Eingangssignals vor. Beispielsweise die Genauigkeit der Messung einer Gleichspannung könnten wir so nicht verbessern. Deshalb ist ein etwas anderer Aufbau, wie in Bild 5.12 gezeigt, zu verwenden.

Zentrales Element des Sigma-Delta-Wandlers ist ein Rauschformer, der bestehend aus einer Differenzstufe, einem Integrator und einem Komparator verschiedene Funktionen wahrnimmt. Zum einen ist die Eingangsgröße des Komparators durch die Differenzbildung jetzt wieder einigermaßen stochastisch gleichverteilt. Zum anderen wirkt der Eingangskreis als Rauschformer, der das Quantisierungsrauschen im höheren Frequenzbereich konzentriert, siehe Bild 5.13 (links).

| Bild 5.13.: | Links: Veränderung des Spektrums des Quantisierungsrauschens durch den Rauschformer. Rechts: Erreichbares Signal-zu-Rausch-Verhältnis SNR in Abhängigkeit von Oversampling-Rate und verwendetem Rauschformer. |

Dies ist besonders willkommen, da so das SNR durch die nachfolgende digitale Filterung („DF“) noch wesentlich effektiver verbessert werden kann. So kann man schon mit einem sehr einfachen Rauschformer erster Ordnung relativ gute Ergebnisse erzielen. Das erreichbare SNR in Abhängigkeit von Rauschformer und Oversampling-Rate ist in Bild 5.13 (rechts) zu sehen. Zum Abschluss der Signalverarbeitung erfolgt noch ein ”Downsampling” („DS“), also die Reduktion der Abtastrate auf die nominelle Abtastfrequenz. Da ja zuvor eine Tiefpass-Filterung stattgefunden hat, ist dies direkt ohne zusätzliche Aliasing-Filter möglich.