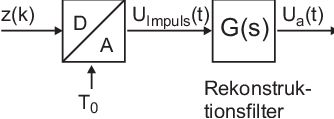

| Bild 7.1.: | Idealisierte D/A-Wandlung und zugehörige Impulsfolge nach Rekonstruktionsfilter |

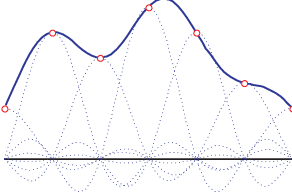

Zu Beginn wollen wir uns jedoch erst mit ein paar Grundlagen der Digital/Analog-Wandlung beschäftigen. Bei der Umwandlung eines zeit- und wertediskreten Signals wird dieses unter idealisierten Bedingungen als Impulsfolge ausgegeben, Bild 7.1. Unter Verwendung eines idealen Rekonstruktionsfilters (idealer Tiefpass) entsteht dann aus der Überlagerung der Impulsantworten das analoge Ausgangssignal.

Da in der realen Welt allerdings die Erzeugung eines Delta-Impulses nicht gelingt (unendlicher Energiegehalt) werden Impulse endlicher Länge mittels eines Haltegliedes für einen Abtastzeitraum konstant ausgegeben, Bild 7.2.

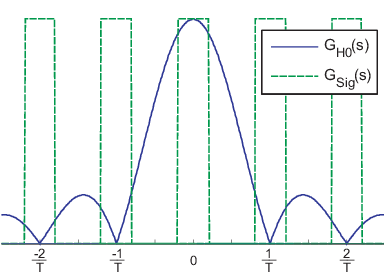

Das zugehörige Frequenzspektrum des Nutzsignals und der Frequenzgang des Halteglieds ist in

Bild 7.3 links zu sehen. Der Frequenzgang des realen Ausgangssignals am Ausgang des

Mikrocontrollers entspricht somit der Überlagerung beider Frequenzgänge, was durch eine

Multiplikation im Frequenzbereich beschrieben werden kann. Das entstehende Spektrum ist im

Basisfrequenzbereich verzerrt und es entstehen zusätzliche Signalanteile an den Spiegelfrequenzen

(um ω0…n ⋅ ω0).

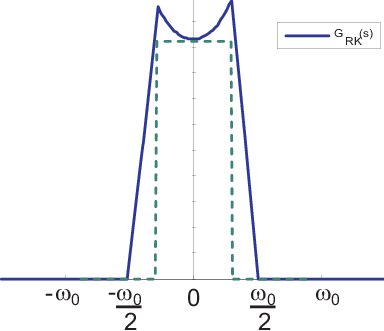

Zur präzisen Rekonstruktion ist zuallererst ein Tiefpassfilter erforderlich, der genau diese störenden Signalanteile an den Spiegelfrequenzen wegfiltert. Der Entwurf dieses Tiefpassfilters erfolgt mit der gleichen Methodik, mit der auch Aliasing-Filter für analoge Eingänge entworfen werden. Zusätzlich beeinflusst das Halteglied auch den Frequenzgang im Nutzsignalband (Dämpfung der höheren Nutzsignalfrequenzen). Dies kann durch ein geeignetes Hochpass-Kompensationsfilter korrigiert werden, Bild 7.3 rechts.

| Bild 7.3.: | Reale D/A-Wandlung links: Spektrum des Nutzsignals und Frequenzgang des Halteglieds. Rechts: Frequenzgang des kompensierenden Rekonstruktionsfilters |

So weit zur signaltheoretischen Betrachtung. Was wir jetzt noch benötigen, ist ein elektrischer

Umsetzer, der aus einer digitalen (abstrakten) Zahl in einem Digitalrechner eine analoge Spannung

erzeugen kann. Nach [TSG02] kann man prinzipiell drei Verfahren der Umsetzung unterscheiden:

Parallelverfahren, Wägeverfahren und Zählverfahren. Deren grundsätzlicher schaltungstechnischer

Aufbau ist in Bild 7.4 gezeigt.

| Bild 7.4.: | Verschiedene Prinzipien der D/A-Wandlung: a)Parallelverfahren, b)Zählverfahren, c)Wägeverfahren |

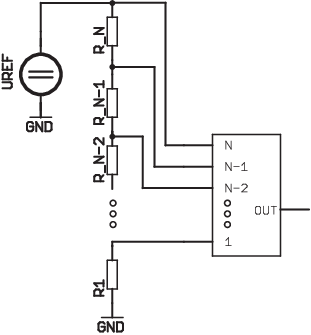

Beim Parallelverfahren werden alle möglichen Ausgangsspannungen parallel erzeugt und die richtige durch einen 1:N Multiplexer ausgewählt, siehe Bild 7.4a). Erwartungsgemäß erfordert diese Realisierung einen extrem großen Aufwand an Bauelementen, die sich in Komplexität und Preis der Umsetzung widerspiegeln. Aus diesem Grunde wird ein solcher Wandler kaum in käuflichen D/A-Wandlern eingesetzt. Vorteil ist die strenge Monotonie der analogen Ausgangswerte, denn die zum nächstkleineren Zahlenwert gehörende Ausgangsspannung ist konstruktionsbedingt immer kleiner als die vorhergehende.

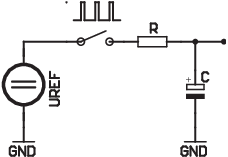

Bei Zähl- oder Zeitmittelwertverfahren wird in Relation zum digitalen Wert eine Referenzspannung in zeitlicher Folge an- und ausgeschaltet, Bild 7.4b). Ein nachfolgendes Filter (hier angedeutet durch einen RC-Tiefpass) glättet die entstehenden Oszillationen und stellt den Ausgangswert her. In der Literatur wird dieses Verfahren auch als Pulsweitenmodulation (PWM) beschrieben. Oftmals wird diese Art der D/A-Umsetzung in Zusammenhang mit schaltenden Leistungshalbleitern (z.B. Mosfets) verwendet, da so die entstehende Verlustleistung extrem gering gehalten werden kann. In Verbindung mit den häufig vorkommenden induktiven Lasten in Kombination mit deren Massenträgheit (z.B. Motoren, Lautsprecher) kann man oft auf die explizite Implementierung des Tiefpassfilters verzichten. Beschränkender Faktor bei diesem Verfahren ist die erreichbare Abtastrate. Um die nötigen Diskretisierungsstufen erzeugen zu können, sind schnelle Zähler erforderlich. So benötigt man für einen 16-Bit-Umsetzer bei einer Abtastfrequenz von 10kHz immerhin einen Zähler mit 655MHz.

Anstelle eines PWM-basierten Ausgangssignals kann man auch binäre Rauschfolgen zum Beispiel aus einem Sigma-Delta-Modulator auf den Schalter ausgeben. Das Prinzip ist ähnlich dem der Sigma-Delta-A/D-Wandlung (siehe Kapitel 5.1), bei der eine Sigma-Delta-Modulationsstufe aus einem Wert eine Impulsfolge formt. Beim D/A-Wandler ist das Eingangssignal des Modulators das digitale Signal. Der Integrator sowie der Komparator sind digital realisiert. Die Ausgangs-Binärfolge wird dann einfach über den digitalen Schalter ausgegeben. Der anschließende Tiefpass ist analog realisiert. Vorteil dieser Umsetzung ist das auch hier auftretende ”Noise-Shaping”, was den erreichbaren Signal-Störabstand im Zusammenspiel mit dem Oversampling günstig beeinflusst. Solche D/A-Wandler sind mittlerweile in vielen CD-Spielern oder anderen digitalen Audioquellen weit verbreitet. Sie werden dort oft als 1-Bit-D/A-Wandler bezeichnet. Bei Verwendung als Lastausgang besteht bei dieser Art der Implementierung aber das Problem entsprechend schnell schaltende Leistungshalbleiter zu finden.

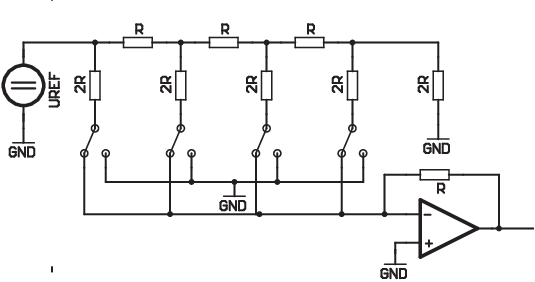

Als letztes Prinzip haben wir das Wägeverfahren, Bild 7.4c). Dies basiert darauf, dass alle

Spannungen von  ⋅ Uref erzeugt werden und selektiv über einen Summationsverstärker

aufsummiert werden können. Deshalb werden für einen n-Bit-Wandler auch genau n Schalter

benötigt. Im Bild werden die verschiedenen Spannungen über ein so genanntes R-2R Leiternetzwerk

aus einer Referenzspannung erzeugt.In einem solchen Netzwerk beträgt die Spannung am nächsten

Knotenpunkt immer die Hälfte der Spannung des vorigen. D/A Wandler dieses Typs sind im

DAC12-Modul des MSP integriert.

⋅ Uref erzeugt werden und selektiv über einen Summationsverstärker

aufsummiert werden können. Deshalb werden für einen n-Bit-Wandler auch genau n Schalter

benötigt. Im Bild werden die verschiedenen Spannungen über ein so genanntes R-2R Leiternetzwerk

aus einer Referenzspannung erzeugt.In einem solchen Netzwerk beträgt die Spannung am nächsten

Knotenpunkt immer die Hälfte der Spannung des vorigen. D/A Wandler dieses Typs sind im

DAC12-Modul des MSP integriert.